Цифровая обработка сигналов в ПЛИС

Курс позволит осуществить "быстрый старт" в имплементации алгоритмов ЦОС на ПЛИС Intel FPGA. В рамках курса представлена информация о принципах работы цифровых блоков управления и обработки сигналов с учётом архитектуры микросхем программируемой логики Intel. Основное внимание в рамках курса уделяется практическим навыкам моделирования и внедрения наиболее распространённых алгоритмов ЦОС - цифровых фильтров, преобразования Фурье, а также блоков управления, в частности ПИД-регуляторов.

| Продолжительность обучения | 2 дня | |

| Место проведения | Санкт-Петербург, Новоизмайловский проспект, 34к3 | |

| Форма обучения | с 10:00 до 17:00 | |

| Стоимость обучения | ~50000 руб * | |

| Контакты | +7(962)722-36-80 / cpe.ifmo@yandex.ru |

Обучение позволит:

- получить основные знания об элементах ЦОС и особенностях их реализации на ПЛИС Intel FPGA

- моделировать и создавать свои алгоритмы ЦОС на ПЛИС

Аннотация курса

- Тема 1

- Введение. Основные понятия ЦОС

- Тема 2

- Цифровые генераторы сигналов

- Тема 3

- Преобразование Фурье

- Тема 4

- Цифровая фильтрация

- Тема 5

- Системы с обратной связью

Необходимые знания:

- наличие представления о ПЛИС фирмы Intel и процессе их проектирования

- желателен начальный опыт проектирования на ПЛИС фирмы Intel

- знание тем курса Основы проектирования на FPGA

Программа курса

| Тема 1 Введение. Основные понятия ЦОС |

Приводится информация об основных понятиях ЦОС, аналоговых и цифровых сигналах. Слушатели знакомятся с форматами данных и способами округления чисел с фиксированной и плавущей точкой, на основе которых реализуются алгоритмы ЦОС на ПЛИС. Описываются принципы работы цифровых блоков обработки сигналов с учётом архитектуры микросхем программируемой логики Intel FPGA. |

| Тема 2 Цифровые генераторы сигналов |

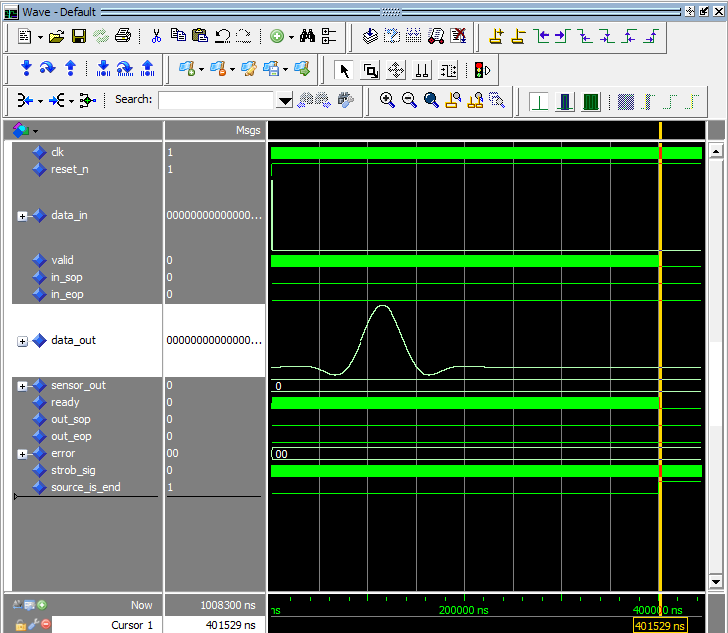

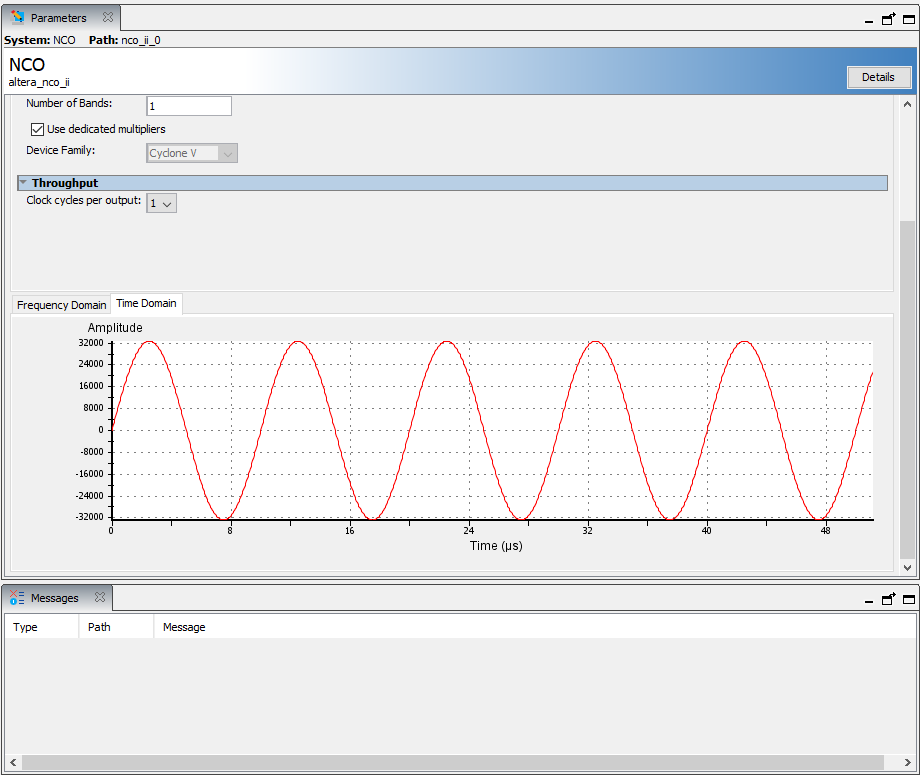

Рассматриваются основные способы реализации цифровых генераторов сигналов на ПЛИС, в том числе создание собственных блоков на языке HDL. Слушатели знакомятся с IP-блоком фирмы Intel FPGA для создания синусоидальных сигналов - numerically controlled oscillator (NCO). Рассматриваются особенности моделирования IP-блоков в среде ModelSim на примере IP-блока NCO. |

| Тема 3 Преобразование Фурье |

Слушателям рассказывают о дискретном преобразовании Фурье (ДПФ) и его применении для построения и анализа спектров сигналов. Рассматривается алгоритм быстрого преобразования Фурье и его реализация на ПЛИС Intel FPGA в виде IP-блока FFT. |

| Тема 4 Цифровая фильтрация |

Рассматриваются фильтры с конечной и бесконечной импульсной характеристикой (КИХ и БИХ фильтры), а также способы их создания, такие как свертка и рекурсивный метод. Описываются различные способы реализации таких фильтров в ПЛИС, в том числе создание собственных блоков на языке HDL. Слушатели знакомятся с IP-блоком для создания КИХ фильтров в ПЛИС фирмы Intel FIR Compiler II. |

| Тема 5 Системы с обратной связью |

Описываются основные понятия систем регулирования и z-преобразования и его применения для анализа систем с обратной связью. Рассматривается система с обратной связью на основе ПИД-регулятора и вопросы по ее реализации на ПЛИС с учетом особенностей форматов данных (с фиксированной и плавущей точкой). |

Лабораторные работы

| Лабораторная работа №1 Создание и реализация генераторов сигналов на ПЛИС |

В лабораторной работе создается проект в среде Quartus Prime, в котором собирается генератор синусоидальных сигналов на основе IP-блока NCO и генератор пилообразного сигнала, реализованного с помощью собственного блока на языке HDL. Функционал проекта проверяется в среде моделирования ModelSim и на отладочной плате с помощью инструмента SignalTap II Logic Analyzer. |

| Лабораторная работа №2 Реализация БПФ в ПЛИС |

В лабораторной работе к генераторам сигналов добавляется блок БПФ на основе IP-блока FFT, проект моделируется в среде ModelSim и проверяется на отладочной плате. |

| Лабораторная работа №3 Фильтрация цифровых сигналов в ПЛИС |

В лабораторной работе собирается проект с несколькими генераторами сигналов на основе IP-блоков NCO и блоком цифрового фильтра FIR Compiler II. Проводится моделирование цифрового фильтра в среде ModelSim. Проект проверяется на отладочной плате с помощью инструмента SignalTap II Logic Analyzer. |

| Лабораторная работа №4 Реализация простой системы регулирования на основе ПИД-регулятора |

В лабораторной работе происходит сборка системы регулирования на основе ПИД-регулятора и ее симуляция с помощью тестовых сигналов. |