Основы проектирования на FPGA

Этот курс дает представление о методах создания эффективного дизайна при разработке проектов на ПЛИС фирмы Xilinx с использованием среды разработки Vivado Design Suite. Делается акцент на организации среды разработки Vivado и ее возможностях. Рассматриваются фундаментальные понятия логического синтеза и особенности временного анализа применительно к линейке ПЛИС Xilinx.

| Продолжительность обучения | 4 дня | |

| Место проведения | Санкт-Петербург, Новоизмайловский проспект, 34к3 | |

| Форма обучения | с 10:00 до 17:00 | |

| Стоимость обучения | ~100000 руб * | |

| Контакты | +7(962)722-36-80 / cpe.ifmo@yandex.ru |

Обучение позволит:

- знать архитектурные ресурсы линейки ПЛИС Xilinx 7-ой серии/Ultrascale/Ultrascale+;

- ориентироваться в доступных в Vivado IDE процессах разработки (design flows);

- ориентироваться в типах файлов (HDL, XDC, simulation);

- анализировать проект с помощью схематичного и иерархичного средств отображения;

- производить синтез и имплементацию HDL-дизайна;

- использовать отчеты для анализа проекта по времени, питанию, занимаемым ресурсам (utilization, timing, power reports);

- создавать специальные программные блоки с использованием библиотеки программных ядер (IP Library utility);

- назначать базовые временные ограничения (basic timing constraints);

- использовать базовые Tcl-отчеты (Tcl-based reports);

- знать особенности синхронной методологии проектирования;

- использовать отчеты встроенного временного анализатора (STA reports);

- знать принципы конфигурации ПЛИС.

Аннотация курса

- Тема 1

- Вводная часть курса

- Тема 2

- Обзор среды Vivado Design Suite

- Тема 3

- Синтез, сборка и временные ограничения в среде Vivado Design Suite

- Тема 4

- Работа с ресурсами ПЛИС 7-ой серии/Ultrascale/Ultrascale+

- Тема 5

- Работа с IP-ядрами в IP Integrator

- Тема 6

- Использование временных ограничений XDC и анализ отчетов производительности проекта по времени

Необходимые знания:

- наличие представления о ПЛИС фирмы Xilinx и процессе их проектирования

- желателен начальный опыт проектирования ПЛИС фирмы Xilinx

Программа курса

| Тема 1 Вводная часть курса |

Вводная часть курса дает представление о существующих ПЛИС фирмы Xilinx 7-ой серии/Ultrascale/Ultrascale+ и о причинах создания новой среды разработки Vivado Design Suite взамен среды ISE Xilinx Design Suite. Так же выделяются основные отличительные черты последнего поколения и новые возможности. |

| Тема 2 Обзор среды Vivado Design Suite |

Демонстрируется интерфейс среды Vivado Design Suite. Описывается процесс создания нового проекта, основные виды отчетов и способы их отображения. Показывается, как можно проанализировать проект с помощью различных средств отображения, и как научиться запускать и использовать инструмент проверки соблюдения перечня предписаний проекта. |

| Тема 3 Синтез, сборка и временные ограничения в среде Vivado Design Suite |

В теме рассматриваются синтез и сборка с учетом временных ограничений, показаны концепции оптимизации дизайна по времени, и методы анализа критических путей с помощью средств отображения Vivado. |

| Тема 4 Работа с ресурсами ПЛИС 7-ой серии/Ultrascale/Ultrascale+ |

В теме описываются архитектурные особенности и доступные ресурсы ПЛИС Xilinx 7-ой серии/Ultrascale/Ultrascale+. Показано, как создавать блоки, использующие встроенные ресурсы ПЛИС, и как задавать оптимальные параметры блоков с учетом архитектуры 7-ой серии/Ultrascale/Ultrascale+. |

| Тема 5 Работа с IP-ядрами в IP Integrator |

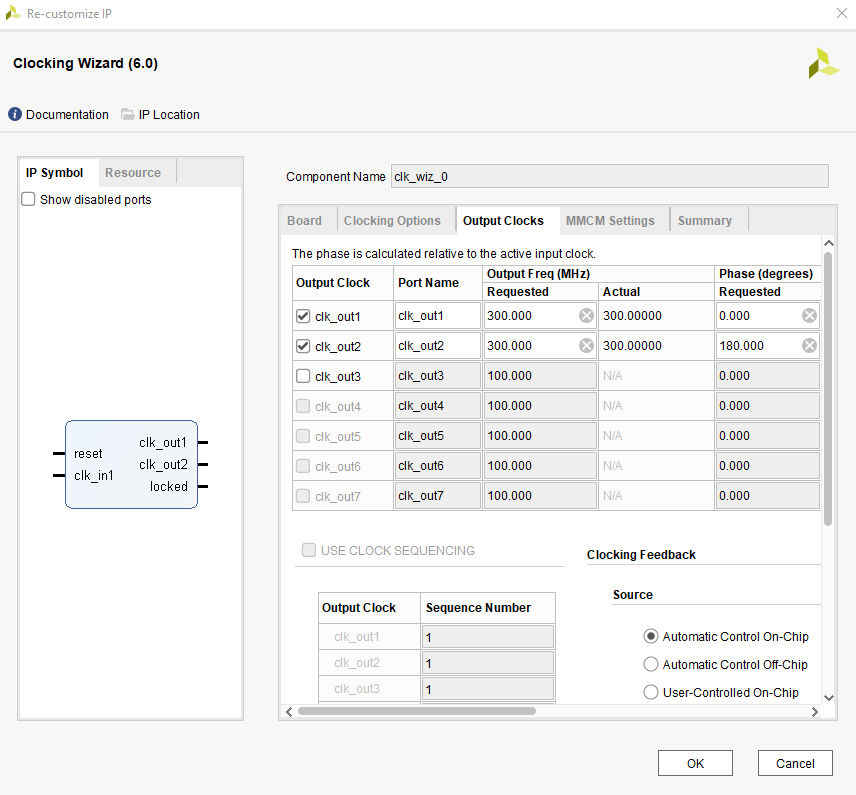

В теме рассматриваются средства интеграции высокоуровневых элементов проекта – Vivado IP Integrator , описываются методы создания сложных систем с помощью Vivado IP Integrator. Так же в теме показаны основные возможности инструмента Vivado IP Integrator и как с помощью него создавать собственные системы. |

| Тема 6 Использование временных ограничений XDC и анализ отчетов производительности проекта по времени |

В теме описывается новый формат файлов ограничений проекта – XDC files. Показано, как создавать собственный файл временных ограничений, как проводить временной анализ проекта с помощью инструмента STA, как проанализировать производительность с помощью отчетов. |

Лабораторные работы

| Лабораторная работа №1 Анализ проекта в среде Vivado Design Suite |

В лабораторной работе создается проект в среде Vivado Design Suite. Производится синтез и сборка проекта. Слушатели знакомятся с типами отчетов и учатся их анализировать. Проект анализируется с помощью различных средств отображения. Демонстрируется работа инструмента проверки соблюдения перечня предписаний проекта. |

| Лабораторная работа №2 Синтез, сборка и временные ограничения в среде Vivado Design Suite |

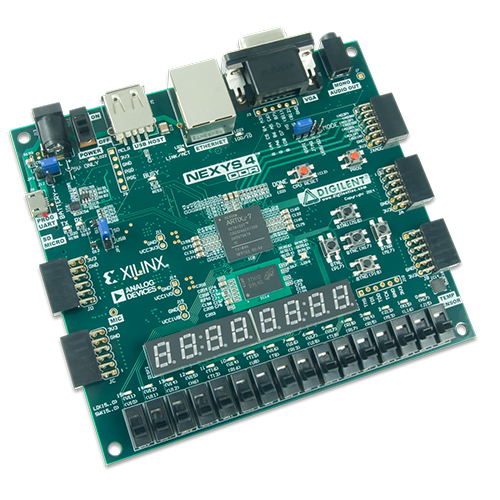

В лабораторной работе детально анализируются результаты синтеза и сборки. Слушатели оптимизируют проект с помощью введения временных ограничений и использования концепции конвейеризации. Описывается процесс анализа критических путей. На каждом этапе оптимизации проекта происходит повторный синтез и сборка и анализируются их результаты. В итоге собирается файл bitstream и прошивается в отладочную плату для демонстрации. |

| Лабораторная работа №3 Работа со встроенными ресурсами ПЛИС |

В лабораторной работе в проект интегрируется блок, использующий встроенные ресурсы ПЛИС. Слушатели учатся настраивать такие блоки и оптимизировать их с учетом особенностей архитектуры ПЛИС Xilinx 7-ой серии/Ultrascale/Ultrascale+. |

| Лабораторная работа №4 Проектирование с использованием IP блоков |

В лабораторной работе с помощью IP Integrator создаются IP блоки и встраиваются в проект. Слушатели учатся создавать сложные системы в IP Integrator и настраивать каждый блок отдельно с помощью Customization Wizard. |

| Лабораторная работа №5 Использование временных ограничений XDC и анализ отчетов производительности проекта по времени |

В лабораторной работе слушатели знакомятся с новым форматом файлов ограничений проекта – XDC files. Слушатели создают собственный файл временных ограничений. Проводят временной анализ с помощью инструмента STA и анализируют производительность системы на основе отчетов. |